Figure-of-Merit (FoM) Optimization in Class-C Oscillators

Alireza Nourbakhsh\*1, Aminghasem Safarian2, and Sanaz Sadeghi3

<sup>1</sup>Department of Electrical Engineering, Sharif Univercity of Technology, Theran, Iran. Tel.: +989195726063, Email: alireza.nourbakhsh@ee.sharif.edu

<sup>2</sup>Department of Electrical Engineering, Sharif Univercity of Technology, Theran, Iran. Tel.: +989125113968, Email: safarian@sharif.edu

<sup>3</sup>Department of Electrical Engineering, Cornell University, Ithaca, NY, USA. Tel.: +16072620477, Email: ss3842@cornell.edu

Abstract—In this paper, a new approach to optimize phase noise and Figure-of-Merit (FoM) in class-C oscillators is presented. This approach recruits DC voltage of the common source node of the switching pair transistors as an indicator to achieve the best performance of a class-C oscillator. The proposed indicator has the advantages of not introducing any loading effect to the output node, and independency from PVT changes. The method is simple and applicable to any oscillator with class-C topology, and with some modifications it would be applied to other oscillator topologies like class-B. The idea is verified using theoretical analysis, and circuit simulations on  $0.18\mu m$  CMOS technology at 2GHz oscillation frequency. Moreover, a discrete prototype is fabricated at 15MHz and measurement results are provided which further validate feasibility of this approach.

*Index Terms*—oscillator, class-C, FoM, phase noise, saturation, triode.

### I. INTRODUCTION

Modern standards for oscillators require high spectral purity, i.e. low phase noise, along with low power consumption. Achieving these specifications together, which is equivalent to maximizing Figure-of-Merit (FoM), is still considerably challenging for oscillator designers. Cross-coupled oscillators are among the most-used topologies in high performance applications due to their good FoM performance. The most common architectures in cross-coupled oscillators are class-B and class-C. Although designing of class-C oscillators is more challenging, they can achieve higher FoM due to lower power consumption. A comparative study between these two architectures is provided in [1].

There have been several works on improving FoM through decreasing phase noise or power consumption in cross-coupled oscillators [2], [3], [4], [5]. For instance some methods like current reuse [6], incorporating a new resonator [7], using Darlington structure [8] and making the tail current source to work in sub-threshold region [9] can be used to lower the phase noise and thus improving the FoM. [10] optimized the sizing of the transistors to maximize the FoM. In [11] and [12] a negative feedback loop is proposed that senses the oscillation amplitude by an amplitude detector and gradually decreases bias voltage of the core transistors to make them work in class-C mode. [13] also used this method to ensure robustness of the oscillator startup. However, this approach loads the tank, decreasing both its quality factor and tuning range of the oscillator. A better approach in [14] takes the feedback from

tail node and adjusts bias voltage of core transistors such that the tail node voltage tracks an external reference voltage, without perturbing the output nodes. In [15] and [16] two feedback loops are used to simultaneously ensure the robust startup and lower the phase noise. [17] used a digitally controlled circuit for the same purpose. However, in all of the above-mentioned works the exact criterion to determine the reference voltage to attain optimum FoM is not clear.

According to [2], forcing the tail node to oscillate at exactly twice the oscillation frequency  $(2f_{\rm osc})$  will minimize the phase noise, so it uses an extra LC filter at the tail node for this purpose. Using this fact, and given that dependency of the output frequency on the tail bias current would be minimum when the tail tank resonates at exactly  $2f_{\rm osc}$ , [18] has proposed a technique to automatically set the tail tank to the desired frequency. A better approach is introduced in [19], taking into account that when the tail tank is trimmed to  $2f_{\rm osc}$ , its voltage reaches the maximum amplitude. Thus, a peak detector is utilized and the variable capacitor bank of the tail tank is adjusted in order to achieve the optimum point of operation. But the common drawback of all these methods is their high sensitivity to any deviation from  $2f_{\rm osc}$ ; based on [19], a 6% error in tail tank would deteriorate the phase noise by 4dB. Also the method in [20] is applicable only when a tank circuit is used in the tail node, therefore cannot be used in typical LC oscillators.

All of the above mentioned methods cease to preserve the optimum performance point in presence of PVT changes. In this paper we introduce a new indicator to achieve the maximum FoM of a class-C oscillator and exploit it to ensure optimum performance in spite of PVT changes. We will focus on class-C oscillator to explain this idea since it demonstrates a better performance than conventional class-B oscillators in terms of phase noise and power consumption [21].

The paper is organized as follows: in section II the important relation between FoM and DC voltage of the tail node ( $V_{\rm S,DC}$ ) will be obtained through theoretical analysis alongside with some intuitive arguments based on fundamental features of the class-C oscillator. Circuit simulations will also be presented to support the idea. Measurement results are presented in section III and finally section IV concludes the paper.

1

### II. CONCEPT DEMONSTRATION

This section presents the main concept of this paper – that is the "dependency of FoM on the DC voltage of the tail node". First, FoM is defined as follows [22]

$$FoM = 20log\left(\frac{f_{osc}}{\Delta f}\right) - L\{\Delta f\} - 10log(P_{DC,mW}), \quad (1)$$

where  $f_{\rm osc}$  is the oscillation frequency,  $\Delta f$  is the offset frequency from  $f_{\rm osc}$ ,  $P_{\rm DC,mW}$  is total power consumption in mW and  $L\{\Delta f\}$  is the phase noise at offset  $\Delta f$ .

For the purpose of this section, first it will be proved that by sweeping the bias current of the oscillator,  $V_{\rm S,DC}$  will have a maximum value in a particular bias point. Then in the next part we will conclude this point is the very optimum bias point which we were looking for.

#### A. Tail Node Voltage Analysis

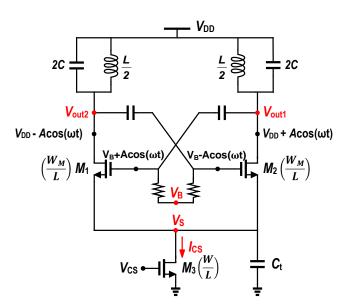

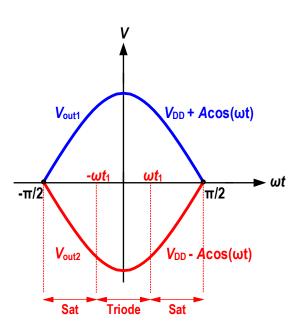

Consider the class-C oscillator shown in Fig. 1 We denote the tail voltage by  $V_{\rm S}$ , bias voltage of core transistors by  $V_{\rm B}$  and single-ended output voltage amplitude by A. Two output nodes have bias voltages of  $V_{\rm DD}$  and a differential signal with amplitude A. Therefore, we can show them in one half-period as Fig. 2, assuming a cosine waveform for each of them. As it is clear, falling  $V_{\rm out-}$  may cause  $M_1$  to operate in triode region for a fraction of this half-period. For this reason, writing the well-known condition for working MOS transistor in triode region,  $V_{\rm D} < V_{\rm G} - V_{\rm th}$ , with  $V_{\rm th}$  being threshold voltage of the transistor for  $M_1$  in this half-period gives

$$V_{\rm DD} - A\cos\omega t < V_{\rm B} + A\cos\omega t - V_{\rm th}.$$

(2)

Assuming  $t_1$  as the transition time of  $M_1$  from saturation to triode we have

$$t_1 = \frac{1}{\omega} \cos^{-1} \left( \frac{V_{\rm DD} - V_{\rm B} + V_{\rm th}}{2A} \right).$$

(3)

This means in this half-period for  $|t| > t_1$ ,  $M_1$  is in saturation region, and for  $|t| < t_1$ ,  $M_1$  would operate in triode, as it is shown in Fig. 2. Of course in the next half-period,  $M_2$  will have this condition. However, if the argument of  $\cos^{-1}$  function in Equation 3 is greater than unity, the equation would be undefined. We can state this condition as

$$A < \frac{V_{\rm DD} - V_{\rm B} + V_{\rm th}}{2}$$

(4)

So if Equation 4 is satisfied, the both transistors will stay in saturation region for their whole conduction time of the period. This is because the oscillation amplitude is too small. Note also that according to [21], A itself is an increasing function of  $I_{\rm CS}$  (the bias current). This means for low values of  $I_{\rm CS}$  which Equation 4 is valid, transistors are totally in saturation region, but higher values of  $I_{\rm CS}$  brings transistors into triode region for a portion of each cycle. Later in this section we will derive an approximate algebraic relation between A and  $I_{\rm CS}$  using simulation results.

KCL (Kirchhoff's Current Law) equation at the tail node of the oscillator shown in Fig. 1 provides (neglecting parasitic device capacitance compared to  $C_{\rm t}$ )

$$I_{\rm D1} + I_{\rm D2} = I_{\rm CS} + C_{\rm t} \frac{dV_{\rm S}}{dt}$$

(5)

If  $V_{\rm B}=V_{\rm th}$ , for half-period of negative voltage swing in gate of a transistor, neglecting subthreshold conduction, that transistor can be assumed off. In our case, the gate AC voltage of  $M_2$  in this half-period is negative, which renders our assumption further reasonable. Hence Equation 5 is simplified to

$$I_{\rm D1} = I_{\rm CS} + C_{\rm t} \frac{dV_{\rm S}}{dt}.$$

(6)

Assuming  $|t| > t_1$  which means  $M_1$  is saturated, Equation 6 turns to

$$\frac{\beta}{2} \times \frac{(V_{\rm B} + A\cos\omega t - V_{\rm S} - V_{\rm th})^2}{1 + \theta(V_{\rm B} + A\cos\omega t - V_{\rm S} - V_{\rm th})} = I_{\rm CS} + C_{\rm t} \frac{dV_{\rm S}}{dt}$$

(7)

with  $\beta = (\mu_{\rm n} C_{\rm ox} W/L)$  being  $\mu_{\rm n}$  electron mobility,  $C_{\rm ox}$  oxide capacitor, W/L ratio of width to length of the transistor. In Equation 7  $\theta$  is the mobility reduction coefficient modeling short channel effects of the transistor. This equation is a first order differential equation for variable  $V_{\rm S}(t,I_{\rm CS})$  with respect to time. Next, we rewrite Equation 6 for  $|t| < t_1$ , when  $M_1$  is in triode (in the case that condition of Equation 4 is not satisfied). So we have

$$\frac{\beta}{2} [2(V_{\rm B} + A\cos\omega t - V_{\rm S} - V_{\rm th})(V_{\rm DD} - A\cos\omega t - V_{\rm S}) - (V_{\rm DD} - A\cos\omega t - V_{\rm S})^2]$$

$$- (V_{\rm DD} - A\cos\omega t - V_{\rm S})^2]$$

$$/ [1 + \theta(V_{\rm B} + A\cos\omega t - V_{\rm S} - V_{\rm th})] = I_{\rm CS} + C_{\rm t} \frac{dV_{\rm S}}{dt} \tag{8}$$

These two differential equations do not have explicit answers, so numerical methods should be exploited. For this purpose, design values defined in Table I and  $V_{\rm B} = V_{\rm th} = 0.52 \, {\rm V}, \, f_{\rm osc} = 2 \, {\rm GHz}, \, \mu C_{\rm ox} = 357.6 \mu {\rm A/V^2}$  and  $\theta = 1$  are substituted in Equation 7 and Equation 8. This will provide the final piece-wise differential equation shown in Equation 9 bellow this page. In this equation,  $V_{\rm B}$  is in Volts,  $I_{\rm CS}$  in mA and t in ns. Only in case  $A < V_{\rm DD}/2 = 0.9 \, {\rm V}$  (according to Equation 4),  $M_1$  will always work in saturation region and  $t_1$  will not exist, so Equation 9 will be defined solely by the first expression. According to Equation 3,  $t_1$  in Equation 9 can be expressed as

$$t_1 = \frac{1}{\omega} \cos^{-1} \left( \frac{V_{\rm DD}}{2A} \right). \tag{10}$$

Equation 9 is also dependent on variable A. So in order to have an equation describing  $V_{\rm S}$  in terms of t and  $I_{\rm CS}$ , the relation between A and  $I_{\rm CS}$  needs to be extracted. Keeping  $V_{\rm DD}$  and  $V_{\rm B}$  constant, A would be just a function of  $I_{\rm CS}$ . For deriving the relation between them, we can use the simple linear formula below.

$$A = R_{\rm p}I_{\omega 0} = R_{\rm p}I_{CS}.$$

(11)

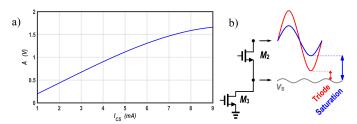

In Equation 11  $R_{\rm P}$  is the whole parasitic resistance in the tank and the fundamental current component passing through the tank equals to the bias current in a class-C oscillator [4]. However, this simple relation does not account for the voltage limited regime shown in Fig. 3(a) where the oscillation amplitude saturates for high bias currents. Thus, a higher order polynomial relation that could model this behavior is required. As such model was not found in any reference, we performed a simulation on the circuit represented in Fig. 1 with  $V_{\rm B} = V_{\rm th} = 0.52 {\rm V}$  and  $f_{\rm osc} = 2 {\rm GHz}$ , to extract the coefficients for the third order polynomial approximation which is provided in below equation.

$$A = -0.0013I_{\text{CS}}^3 + 0.0078I_{\text{CS}}^2 + 0.2228I_{\text{CS}} - 0.032 \tag{12}$$

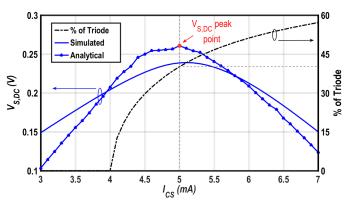

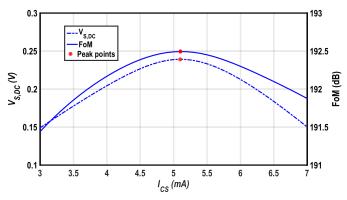

Now the final piece-wise two-variable differential equation can be driven by substituting Equation 10 and Equation 12 in Equation 9. Numeric solvers in Matlab have been used to obtain  $V_{\rm S}(t)$  function for each bias current ( $I_{CS}$ ) with 0.1mA current step. Finally the average of  $V_{\rm S}(t)$  ( $V_{\rm S,DC}$ ) which is achieved in this way is plotted in Fig. 4. The boundary condition in Equation 4 for  $V_{\rm B} = V_{\rm th}$  can be written as  $A = V_{\rm DD}/2 = 0.9$ , which according to Equation 12 occurs at  $I_{\rm CS} = 4 \, \rm mA$ . At this point, core transistors start entering triode region when the oscillation amplitude reaches its peak. As it is clear from Fig. 4, after this point the percentage of a period in which the core transistors work in triode region starts to increase. A key observation from the curve in Fig. 4 is that at the peak point of the analytical  $V_{S,DC}$ , the core transistors are in triode region in 40% of their conduction period and the bias current is  $I_{\rm CS} = 5 \, {\rm mA}$ , a little more than the boundary value of 4mA. This significant point will be deliberated more carefully in the next section.

Simulated  $V_{\rm S,DC}$  is also plotted in Fig. 4 for comparison. The key point is coincidence of peaks of these two curves with a good approximation. But there is some mismatches between their levels, which can be linked to model simplifications such as neglecting channel length modulation and effects of working in high frequencies. Nevertheless, the simulated curve trend is well approximated by the analytical one.

# B. Finding the optimal point

By optimal point in this section we mean the maximum FoM point, and we are going to show the maximum  $V_{\rm S,DC}$  is this optimal point. Shown in Fig. 3(a) as the bias current increases, the output voltage amplitude is also grows up. So there will be a point at which each core transistor enters triode region while reaching its negative peak drain voltage, as it is illustrated in Fig. 3(b). For low values of bias current, core transistors are always in saturation region, and output voltage amplitude is a linear function of bias current [21]. However, for high values of bias current, each core transistor enters triode region for a fraction of its conduction period. This enforces output amplitude to saturate gradually. It also has been emphasized in [21] that the phase noise would not be impaired if core transistors only *moderately* (and *not deeply*) enter triode region. In this work we quantify moderate and deep triode as the percentage of a period in which the core transistors are in the triode region. In the peak of analytical  $V_{\rm S,DC}$  (see Section II-A) this percentage was 40% and the associated bias current was 5mA. So this has to be an approximate standard for deep triode region (of course for our setup and element values), as we will show in this section.

Four significant phenomena which directly affect the phase noise and FoM behavior of a class-C oscillator are mentioned below. The main common feature among all of them is starting their effect in the *boundary* of saturation and triode regimes, and completing it in *deep* triode region.

*First*: as it can be seen from Fig. 1, there is a large capacitance in class-C oscillator from tail node to the ground, creating a low

impedance path for tank circuit if core transistors become triode, which adversely effects both tank quality factor and phase noise generated by the transistors. Commonly this is referred to as "Q-degradation" effect [2].

Second: Referred to [21], by entering transistors in triode region, their conduction time (i.e. time which their current is non-zero) grows up. And since a transistor contributes noise only when it is conducting, their total noise also increases. In fact, this shows the benefit of working in class-C topology while transistors are kept in their active region; since the conduction time is very small, ideally near zero, their contribution to the phase noise is minimal, even negligible. One may justify this effect also in terms of Noise Modulation Function (NMF) in ISF theory [23]. Using this theory, [21] has shown that the effective ISF of the switching transistor shows a huge increment when these transistors enter triode region. Noting that the transistors' ISFs do not show a considerable change, we can link this transition to their NMFs, which have a direct dependency on their conduction time.

*Third*: The main superiority of class-C over class-B is its impulse-like currents [21], which will be vanished if core transistors enter triode region.

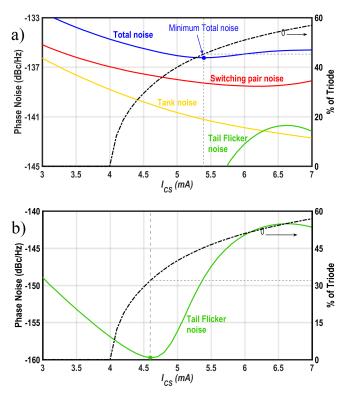

Forth: The switching pair noise and the Flicker noise of the tail transistor contribute significantly to the total phase noise when the core transistors work in triode region for a considerable portion of oscillation period. To illustrate this, we conducted a noise contribution simulation on the circuit of Fig. 1. Fig. 5 shows the simulation results. The circuit oscillates at  $f_{\rm osc} = 2 {\rm GHz}$  and phase noise has been obtained at 1MHz offset and is plotted versus the bias current  $I_{\rm CS}$ . Noting Fig. 5(a), noise of tank circuit barely has an effect on the total noise behavior, as its decreasing trend does not change once the core transistors enter triode. In this case, noise behavior is defined mostly by the tail transistor's Flicker noise and the core transistors' thermal noise; the tail Flicker noise was totally negligible in low bias currents (see Fig. 5(b)), whereas becomes an effective contributor in high bias currents. [20] has used Groszkowski effect ([24]) to justify this phenomenon and referred to it as "Incremental Groszkowski" effect. It has shown that the mentioned effect occurs only at high bias currents, where the oscillator is working in voltage limited regime (see Fig. 3(a)), and core transistors have entered triode region. Under this condition, Flicker noise of the tail current source can be converted to phase noise through Incremental Groszkowski effect, whereas in low bias currents this mechanism is absent which is consistent with the noise contribution result shown in Fig. 5. Also the switching pair noise is the most determinant part especially when it gets the increasing trend in high bias currents (deep triode region). Now we wish to take a closer look at Fig. 5. From Fig. 5(a) it can be inferred that at the minimum total phase noise point, the core transistors work in triode region for 45% of their conduction period. In the previous section, we obtained 40% as the triode percentage of core transistors in analytical  $V_{\rm S,DC}$  peak point (which has to be the maximum FoM point). How can this 5% difference be interpreted? To answer this question, first note that the maximum FoM always

$$\frac{dV_{S}}{dt} = \begin{cases}

\frac{2.98(A\cos 4\pi t - V_{S})^{2}}{1+1(A\cos 4\pi t - V_{S})} - \frac{I_{CS}}{10} & |t| \ge t_{1} \\

\frac{2.98[2(A\cos 4\pi t - V_{S})(1.8 - A\cos 4\pi t - V_{S}) - (A\cos 4\pi t - V_{S}) - (1.8 - A\cos 4\pi t - V_{S})^{2}]}{1+1(A\cos 4\pi t - V_{S})} - \frac{I_{CS}}{10} & |t| < t_{1}

\end{cases}$$

(9)

happens in a lower bias current than the minimum phase noise; since it also depends on power consumption which increases linearly with the bias current. So starting from the minimum phase noise point ( $I_{\rm CS}=5.4{\rm mA}$ ), the  $I_{\rm CS}$  is deceased by 0.1mA current step. At each point,  $\Delta {\rm FoM}_+$  (FoM increment due to less power consumption) and  $\Delta {\rm FoM}_-$  (FoM decrement due to more phase noise) will be calculated and compared using the following formulas.

$$\begin{split} &\Delta \text{FoM}_{+} = 10 [\log(V_{\text{DD}}I_{\text{CS}} - \log(V_{\text{DD}}(I_{\text{CS}} - 0.1\text{mA})] \\ &= 10 \log(\frac{I_{\text{CS}}}{I_{\text{CS}} - 0.1}) \cong 10 \log(1 + \frac{0.1}{I_{\text{CS}}}) \cong \frac{1}{I_{\text{CS}} \times \ln 10} \end{split} \tag{13}$$

$$\Delta \text{FoM}_{-} = \Delta \text{PN}_{+} \tag{14}$$

In Equation 13 we have assumed the bias current in each step is decreased from  $I_{\rm CS}$  to  $I_{\rm CS}-0.1{\rm mA}$  and then twice using the Taylor approximation provides  $1/(I_{\rm CS}\times {\rm ln}10)$  for  $\Delta {\rm FoM}_+$ . Also Equation 14 states that the FoM decrement is directly equal to the phase noise increment. The results are provided in Table II. According to this table decreasing  $I_{\rm CS}$  until 5mA improves the FoM, but further lowering will start to deteriorate it. Therefore, the optimal bias current is 5mA, equal to that extracted from the analytical curve of Fig. 4 in the Section II-A. So maximum FoM happens at the bias current which maximizes  $V_{\rm S,DC}$ .

Finally, Fig. 6 shows the simulated  $V_{\rm S,DC}$  and the FoM versus bias current. Exact coincidence of peaks of these two curves again verifies the validity of our concept.

#### III. SIMULATED AND MEASUREMENT RESULTS

In order to provide an evidence for the integrity of the proposed idea, a proof-of-concept class-C oscillator prototype (based on Fig. 1) using discrete components is fabricated. The discrete transistors used in the oscillator are FDN335N by ON-Semi corporation. The values of tank capacitor and inductor are  $C=1\mathrm{nF}$  and  $L=100\mathrm{nH}$ . Hence the calculated oscillation frequency becomes  $f_{\mathrm{osc}}=15.9\mathrm{MHz}$ , but the measured oscillation frequency is between the range of 14MHz to 15MHz (varies by the bias current) due to parasitic capacitance of the active devices.

A photograph of the implemented PCB is shown in Fig. 7. Component names are corresponding to Fig. 1. Output signals (including output oscillator voltage and common source node voltage) are shown in red and input signal  $V_{\rm CS}$  (bias voltage of the current source transistor for controlling  $I_{\rm CS}$ ) is shown in blue. Three op-amps (AD8021 by Analog Devices) have been used as buffers to isolate output signals from the oscillator and drive the  $50\Omega$  input impedance of measurement equipment.

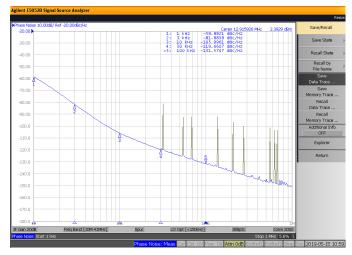

To provide measurement data supporting previous claims, the bias current of the oscillator has been swept by varying the gate bias voltage of the current source transistor ( $V_{\rm CS}$ ) within the oscillator operational range. The gate bias of the core transistors ( $V_{\rm B}$ ) has been fixed to 1V. For each  $V_{\rm CS}$ , the associated phase noise has been measured with Agilent E5052B Signal Source Analyzer in 1kHz to 1MHz offset frequency range. For instance, the measured phase noise with  $V_{\rm CS} = 1.5 \rm V$  is shown in Fig. 8.

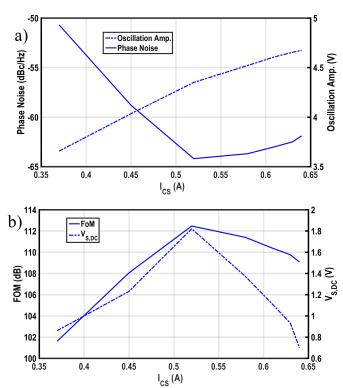

The measurement results are provided in Fig. 9. The oscillation amplitude (parameter A in previous discussions) is plotted in Fig. 9(a). The gradual saturation trend in oscillation amplitude is obvious from this figure. Also the phase noise in 1kHz offset is measured

and shown in the same plot. For  $V_{\rm CS} = 1.3 \rm V$ , the phase noise has its minimum. In Fig. 9(b), the FoM and  $V_{\rm S,DC}$  are plotted along the same interval of  $V_{\rm CS}$ . This plot demonstrates both FoM and VS,DC have their maximum values at  $V_{\rm CS} = 1.3 \rm V$  point. So  $V_{\rm S,DC}$  reaches to its peak when the FoM is maximum, and this is the optimal point of operation for oscillator. This confirms the idea through paper. This graph also shows that optimizing the bias current in this case can lead to 10dB improvement in FoM.

Furthermore, the simulated FoM of the oscillator in Fig. 1 with values in Table I which is shown in Fig. 6 (with the maximum point of 192dB) has been compared with some simulated FoM of previous works, and the result is expressed in Table III. Also, referred to Fig. 6 optimizing the bias current can lead to 1dB FoM improvement in the shown interval. Extensive simulations show that in other technology corners this improvement can be increased up to 6dB.

#### IV. FUTURE WORK

Using the proposed idea as the criterion, a robust self-optimized oscillator may be designed using a feedback loop that maximizes DC voltage of the tail node in order to gain the maximum achievable FoM. If the frequency of the feedback loop is considerably lower than the frequency of the oscillator itself, then in each period of the oscillator its bias remains unchanged and so the oscillator would be stable. Therefore, if the oscillator works in GHz, then a several KHz feedback loop (updating the bias point in less than 1ms) guarantees that the oscillator remains stable.

#### V. CONCLUSION

A novel way to gain the maximum FoM from a class-C oscillator with the related theoretical analysis has been presented in this paper. The validity of this approach has been confirmed through both simulation and measurement results. The new idea, unlike some of the mentioned literatures does not introduce any loading effect on the output tank and is also authentic in any PVT situations. The feedback loop designed based on the proposed idea can be added to any previous work on class-C oscillator to optimize its bias point and FoM.

# REFERENCES

- Mansour M., Zekry A., K. Ali M., et al. "A comparative study between Class-C and Class-B quadrature voltage-controlled power oscillator for multi-standard applications". *Microelectronics Journal*, 98:104726, Apr. 2020.

- [2] Hegazi E., Sjoland H., and Abidi A. "A filtering technique to lower LC oscillator phase noise". *IEEE Journal of Solid-State Circuits*, 36(12):1730–1740, Jul. 2013.

- [3] Teymoori H., Fotowat Ahmady A., and Nabavi A. "A new low phase noise LC-tank CMOS cascode Cross-coupled oscillator". *IEEE J. Iranian Conference on Electrical Engineering*, May 2010.

- [4] Okada K., Nomiyama Y., Murakami R., et al. "A 0.114-mW dual-conduction class-C CMOS VCO with 0.2-V power supply". Symposium on VLSI Circuits, Jun 2009

- [5] Fanori L., Liscidini A., and Andreani P. "A 6.7-to-9.2GHz 55nm CMOS hybrid class-B/class-C cellular TX VCO". *IEEE International Solid-State Circuits Conference*, Feb. 2012.

- [6] Lim C., Ramiah H., Yin J., et al. "A 5.1-to-7.3 mW, 2.4-to-5 GHz Class-C Mode-Switching Single-Ended-Complementary VCO Achieving >190 dBc/Hz FoM". *IEEE Transactions on Circuits and Systems II: Express Briefs*, 66(2):237–241, Jun. 2018.

- [7] Sheikhahmadi S., Moezzi M., and Ghafoorifard H. "A Low Phase Noise Class-C Oscillator With Improved Resonator and Robust Start-Up". IEEE Transactions on Circuits and Systems II: Express Briefs, 68(1):92–96, Jun. 2020.

- [8] Cheng X., Chen F., Xia X., et al. "A Modified Darlington-Based Class-C VCO With Simultaneous Optimization of Phase Noise/FoM in GaAs Technology". IEEE Microwave and Wireless Components Letters, 30(5):500–503, Apr. 2020.

- [9] Shasidharan P., Ramiah H., and Rajendran J. "A 2.2 to 2.9 GHz Complementary Class-C VCO With PMOS Tail-Current Source Feedback Achieving – 120 dBc/Hz Phase Noise at 1 MHz Offset". *IEEE Access*, 7:91325–91336, Jul. 2019

- [10] Martins R., Lourenco N., Horta N., et al. "Many-Objective Sizing Optimization of a Class-C/D VCO for Ultralow-Power IoT and Ultralow-Phase-Noise Cellular Applications". *IEEE Transactions on Very Large Scale Integration* (VLSI) Systems, 27(1):69–82, Oct. 2018.

- [11] Deng W., Okada K., and Matsuzava A. "A feedback class-C VCO with robust start-up condition and enhanced oscillation swing". *Proceedings of* the ESSCIRC, Sep. 2011.

- [12] Chen J., Jonsson F., Calrsson M., et al. "A low power, startup ensured and constant amplitude class-C VCO in 0.18μmCMOS". *IEEE Microwave and Wireless Components Latters*, 21(8):427–429, Jul. 2011.

- [13] Jang S. and Wang J. "Low-phase noise Class-C VCO with dynamic body bias". *Electronics Letters*, 53, May. 2017.

- [14] Fanori L. and Andreani P. "Low-phase-noise 3.4-4.5 GHz dynamic-bias class-C CMOS VCOs with a FoM of 191 dBc/Hz". Proceedings of the ESSCIRC, Sep. 2012.

- [15] Thakkar A., Theertham S., Mirajkar P., et al. "A 3.9–4.5GHz class-C VCO with accurate current injection based on capacitive feedback". 12th European Microwave Integrated Circuits Conference (EuMIC), pages 224–227, Oct. 2017.

- [16] Liao X. and Liu L. "A Low-Voltage Robust Class-C VCO With Dual Digital Feedback Loops". *IEEE Transactions on Circuits and Systems II: Express Briefs*, 67(11):2347–2351, Feb. 2020.

- [17] Lee J., Kim G., Ko G., et al. "Low Phase Noise and Wide-Range Class-C VCO Using Auto-Adaptive Bias Technique". *Electronics* 2020, 9(8), Aug. 2020.

- [18] Wu T., Moon U., and Mayaram K. "Dependence of LC VCO oscillation frequency on bias current". *IEEE International Symposium on Circuits and Systems*, May. 2006.

- [19] Bhat A. and Krishnapura N. "A tail-resonance calibration technique for wide tuning range LC VCOs". *IEEE International Symposium on Circuits and Systems*, May. 2016.

- [20] Nikpaik A. and Nabavi A. "Analysis of flicker noise conversion to phase noise in CMOS differential LC oscillators". *International Journal of Circuit Theory* and Applications, Apr. 2015.

- [21] Mazzanti A. and Andreani P. "Class-C harmonic CMOS VCOs, with a general result on phase noise". *IEEE Journal of Solid-State Circuits*, 43(12):2716–2729, Dec. 2008.

- [22] Fanori L. and Andreani P. "Highly efficient class-C CMOS VCOs, including a comparison with class-B VCOs". *IEEE Journal of Solid-State Circuits*, 48(7):1921–1930, Dec. 2001.

- [23] Lee T. and Hajimiri A. "Oscillator phase noise: a tutorial". IEEE Journal of Solid-State Circuits, 35(3):326–336, Mar. 2000.

- [24] Groszkowski J. "The interdependence of frequency variation and harmonic content, and the problem of constant-frequency oscillators". *Proceedings of* the IRE, 21(7):958–981, 1993.

#### VI. BIOGRAPHIES

**Alireza Nourbakhsh** received B.Sc. and M.Sc. degrees in electrical engineering from Sharif University of Technology, Tehran, Iran, in 2017 and 2019, respectively. He is currently pursuing a Ph.D. degree in electrical engineering with Digital Electronics Group, CSharif University of Technology, Tehran, Iran.

Aminghasem Safarian (Member, IEEE) received the B.Sc. and M.Sc. degrees in electrical engineering from the Sharif University of Technology in 2000 and 2002, respectively, and the Ph.D. degree from the University of California at Irvine, Irvine, in 2006. From 2005 to 2015, he worked with Broadcom Corporation as a Principal Scientist. Currently, he is an Assistant Professor with the Sharif University of Technology. His main research interests are RF/analog integrated circuits and systems design.

**Sanaz Sadeghi** (Member, IEEE) received B.Sc. and M.Sc. degrees in electrical engineering from Sharif University of Technology, Tehran, Iran, in 2015 and 2017, respectively. She is currently pursuing a Ph.D. degree in electrical and electronics engineering with Molnar Group, Cornell University, Ithaca, NY, USA.

## VII. LIST OF CAPTIONS

Fig. 1: Class-C oscillator Schematic for the following analysis.

Fig. 2: One half-period of output voltages of the oscillator shown in Fig. 1; blue: out+, red: out-.

Fig. 3: (a) The typical relation between oscillation amplitude (A) and bias current  $(I_{CS})$ ; (b) illustration of entering core transistors into triode region for high values of oscillation amplitude and  $I_{CS}$ .

Fig. 4: Analytical DC voltage of the tail node  $(V_{\rm S,DC})$  versus bias current  $(I_{\rm CS})$  and the simulated one with design values of Fig. 1 (left axis), and the percentage of a period in which transistors are in triode region (right axis).

Fig. 5: (a) Noise contribution simulation results in circuit of Fig. 1. Center frequency is 2GHz and the design variables are specified in Fig. 1.  $V_{\rm B}$  is set close to  $V_{\rm th}$ . (b) the tail flicker noise with full dimension.

Fig. 6: Simulated FoM and  $V_{\rm S,DC}$  versus  $I_{\rm CS}$  in the circuit of Fig. 1. Center frequency is 2GHz with design variables specified in Fig. 1 and  $V_{\rm B}\!\cong\!V_{\rm th}$ .

Fig. 7: PCB photograph from the implemented class-C prototype oscillator.

Fig. 8: Measured phase noise of the prototype with Agilent E5052B Signal Source Analyzer at 1kHz to 1MHz offset, with  $V_{\rm B}\!=\!1.5{\rm V}$ . A 20dB attenuator is used to protect the Signal Source Analyzer, so the carrier power should be added with 20dB. Also note that this result is obtained for single ended output. Differential output phase noise values would be 3dB lower due to doubling the output power.

Fig. 9: Measured (a) oscillation amplitude and phase noise, (b) FoM and  $V_{\rm S,DC}$  of the prototype oscillator.

Table 1: Values of class-C oscillator circuit in Fig. 1.

Table 2: Transferring from the minimum phase noise point  $(I_{\rm CS}=5.4{\rm mA})$  to the maximum FoM point  $(I_{\rm CS}=5{\rm mA})$ .

Table 3: Comparison with previous works.

TABLE III: Comparison with previous works

|           | Tech. (nm) | Freq. (GHz) | FoM (dB) |

|-----------|------------|-------------|----------|

| This work | 180        | 2           | 192.5    |

| [1]       | 130        | 2.68        | 192      |

| [7]       | 130        | 3.4         | 188.1    |

| [3]       | 180        | 1           | 186.4    |

| [19]      | 65         | 10.8        | 190-191  |

TABLE II  ${\rm TRANSFERRING~FROM~THE~MINIMUM~PHASE}$  Noise point (  $I_{\rm CS}\!=\!5.4{\rm mA})$  to the maximum FoM point (  $I_{\rm CS}\!=\!5{\rm mA})$

| Change of<br>Current (mA) | $\Delta 	ext{FoM}_+$ | $\Delta { m FoM}_{-}$ | FoM<br>Trend |

|---------------------------|----------------------|-----------------------|--------------|

| $5.4 \rightarrow 5.3$     | 0.080 dB             | 0.01 dB               | <b>†</b>     |

| $5.3 \rightarrow 5.2$     | 0.082 dB             | 0.03 dB               | <b>↑</b>     |

| $5.2 \rightarrow 5.1$     | 0.084 dB             | 0.06 dB               | <b>↑</b>     |

| $5.1 \to 5.0$             | 0.085 dB             | 0.07 dB               | <b>↑</b>     |

| $5.0 \to 4.9$             | 0.087 dB             | 0.10 dB               | <b>+</b>     |

Fig. 1: Class-C oscillator Schematic for the following analysis.

TABLE I: Values of class-C oscillator circuit in Fig. 1

|   | TIBLE I. Values of class C oscillator circuit in Fig. 1 |                                          |                       |                            |                       |  |  |  |

|---|---------------------------------------------------------|------------------------------------------|-----------------------|----------------------------|-----------------------|--|--|--|

|   | $V_{\mathrm{DD}}\left(\mathbf{V}\right)$                | $V_{\mathrm{th}}\left(\mathbf{V}\right)$ | C (pF)                | L (nH)                     | $C_{\mathrm{t}}$ (pF) |  |  |  |

|   | 1.8                                                     | 0.52                                     | 2.3                   | 2.7                        | 10                    |  |  |  |

| ĺ | L (Technology) (µm)                                     |                                          | $W_{ m M}$ ( $\mu$ m) | $oldsymbol{Q}$ of inductor |                       |  |  |  |

|   | 0.18 (CMOS)                                             |                                          | 30                    | 14                         |                       |  |  |  |

Fig. 2: One half-period of output voltages of the oscillator shown in Fig. 1; blue: out+, red: out-.

Fig. 3: (a) The typical relation between oscillation amplitude (A) and bias current  $(I_{\rm CS})$ ; (b) illustration of entering core transistors into triode region for high values of oscillation amplitude and  $I_{\rm CS}$ .

Fig. 4: Analytical DC voltage of the tail node  $(V_{\rm S,DC})$  versus bias current  $(I_{\rm CS})$  and the simulated one with design values of Fig. 1 (left axis), and the percentage of a period in which transistors are in triode region (right axis).

Fig. 5: (a) Noise contribution simulation results in circuit of Fig. 1. Center frequency is 2GHz and the design variables are specified in Fig. 1.  $V_{\rm B}$  is set close to  $V_{\rm th}$ . (b) the tail flicker noise with full dimension.

Fig. 6: Simulated FoM and  $V_{\rm S,DC}$  versus  $I_{\rm CS}$  in the circuit of Fig. 1. Center frequency is 2GHz with design variables specified in Fig. 1 and  $V_{\rm B}\!\cong\!V_{\rm th}$ .

Fig. 7: PCB photograph from the implemented class-C prototype oscillator.

Fig. 8: Measured phase noise of the prototype with Agilent E5052B Signal Source Analyzer at 1kHz to 1MHz offset, with  $V_{\rm B}\!=\!1.5{\rm V}$ . A 20dB attenuator is used to protect the Signal Source Analyzer, so the carrier power should be added with 20dB. Also note that this result is obtained for single ended output. Differential output phase noise values would be 3dB lower due to doubling the output power.

Fig. 9: Measured (a) oscillation amplitude and phase noise, (b) FoM and  $V_{\rm S,DC}$  of the prototype oscillator.