# Sharif University of Technology

#### Scientia Iranica

Transactions D: Computer Science & Engineering and Electrical Engineering https://scientiairanica.sharif.edu

# A look-up table based method for voltage balancing of neutral-point in five-level ANPC converter

# Hamidreza Pairo<sup>a,\*</sup> and Mohammad Farzi<sup>b</sup>

- a. Electrical Machines Research Department, Niroo Research Institute, Tehran, Iran.

- b. Iranian Research Institute of Electrical Engineering (IRIEE), ACECR, Tehran, Iran.

Received 16 September 2021; received in revised form 28 September 2022; accepted 11 April 2023

#### **KEYWORDS**

Multilevel inverter; Space Vector Modulation (SVM); Active Neutral Point Clamped (ANPC); Voltage balancing; Motor drive. Abstract. In this paper, an easily implementable method based on look-up tables is presented for balancing the Neutral-Point (NP) voltage in a five-level "Active Neutral Point Clamped (ANPC)" topology for Space Vector Modulation (SVM). In the proposed method, by utilizing the direction of output phase currents, operating region is divided into six zones. In each zone, there are two look-up tables; one for increasing the NP voltage and the other for decreasing the NP voltage. Since some look-up tables in different zones are identical, six individual look-up tables are obtained for controlling the NP voltage. In the proposed method, just few comparative operators and six look-up tables are utilized; therefore this method has proper implementation capability. Also, the proposed method is experimentally implemented on an ANPC converter which drives an induction motor via Rotor Field Oriented Control (RFOC) method. Experimental results verify performance, good dynamic response and effectiveness in balancing the NP voltage in low and high modulation index.

© 2024 Sharif University of Technology. All rights reserved.

#### 1. Introduction

According to proper harmonic spectrum, reduction of rated value of devices, reduction of switching frequency and low  $\frac{dv}{dt}$ , multilevel converters are widely used in high power and high voltage applications which are utilized in industries such as petrochemical, traction, mining, FACTS, marine applications, etc [1–6].

In higher number of levels, both of Neutral-

Point Clamped (NPC) and flying capacitor converters have the problem of balancing the capacitors (dc-link capacitors for NPC and flying capacitors for flying capacitor converters). Recently, several works have been done on balancing the capacitors in NPC [7–10], flying capacitor [11,12] and modular multilevel [13–15] topologies.

The five-level Active Neutral Point Clamped (ANPC) is one of the most attractive topologies between multilevel converters. As described in [16], the overall switch utilization is low in NPC converters which can lead to limitation of output power. To

#### To cite this article:

H. Pairo and M. Farzi "A look-up table based method for voltage balancing of neutral-point in five-level ANPC converter",  $Scientia\ Iranica\ (2024),\ 31(21),\ pp.\ 1981-1993$

https://doi.org/10.24200/sci.2023.59080.6050

<sup>\*.</sup> Corresponding author. Tel.: +98 21 88590143 E-mail address: hpairo@nri.ac.ir (H. Pairo)

overcome this drawback, the NPC Voltage Source Converter (VSC) is extended to the ANPC VSC [16–18].

Different modulation methods have been utilized for ANPC VSC [19-22]. In [19], a universal carrier-based PWM design method through hierarchical decomposition concept is proposed to overcome the increasing PWM design complexity of multilevel converter with a high number of output levels. An optimized PSPWM method is proposed in [20]. Also in this paper, an optimized Neutral-Point (NP) potential balance method is proposed, which can make a trade-off between the NP potential balance and the harmonic performance. In [21], a Common-Mode Voltage (CMV) reduction strategy based on Phase-Shifted Pulse-Width Modulation (PS-PWM) is proposed for ANPC converter, which can realize the NP voltage and the Flying Capacitor (FC) voltages balance. In [22], a novel Space-Vector Pulse Width Modulation (SVPWM) technique for a Five-Level Active Neutral-Point Clamped (5L-ANPC) inverter is proposed to eliminate the CMV.

Also, different methods are presented which focus on balancing the voltages of DC-link and flying capacitors [23–29]. In [25], a method for balancing the DClink and flying capacitors is presented in a situation that phase-shifted modulation is utilized. method, an optimum zero-sequence voltage is calculated to regulate the NP potential. The voltage across the flying capacitors is also regulated by adjusting the switching duty cycles of two PWM signals, which varies the operation time of redundant switching states in each switching period. Also, in [26], for a carrierbased PWM strategy, the voltage balancing across the flying capacitors is achieved by using a proper selection of redundant switching states, and the NP voltage is controlled by the classical dc offset injection. In Selective Harmonic Elimination Pulse-Width Modulation (SHEPWM), both the voltage across the flying capacitors and the dc-link neutral point can be balanced by a small change in the switching angles, which is decided upon the voltage across the lower dclink capacitor, the voltage of the flying capacitor and the direction of the load current [27]. The proposed strategy in [28] analyses all vectors characteristics and computes the vector durations based on the NP voltage difference, which can flexibly balance the NP voltage. Also, a simple method is presented in [29]; this voltage balancing control is achieved by carrying out a proper selection of the switching signals of the converter taking into account the actual values of the flying capacitor voltage and the phase current.

In this paper, a method is proposed in order to achieve a simple method with proper performance in neutral point voltage balancing for five-level ANPC which can be combined with Space Vector Modulation (SVM). In the proposed method, according to the

direction of three-phase currents, the operating area is divided into six different zones. In each zone, two different look-up tables are determined; one for increment of NP voltage and the other for decrement of NP voltage. Since some look-up tables in different zones are identical, six individual look-up tables are obtained for controlling the NP voltage. Afterwards, the proper look-up table would be selected based on the direction of three phase currents and the need for increment/decrement of NP voltage; utilization of this look-up table in selecting the proper output voltage vector leads to balancing the NP voltage. The main advantages of the proposed method for dc-link voltage balancing of ANPC converter are less computational complexity and simplification of implementation. It should be noted that all of operations for dc-link voltage balancing includes basic logic operators such as and, or, not, etc.

In this paper, at first, multilevel SVM and the method of balancing the flying capacitor voltages are presented in Sections 2 and 3. Afterwards, the proposed method of balancing the NP voltage is presented in Section 4. Finally, the proposed method performance is evaluated by experimental results in Section 5.

#### 2. Multilevel SVM

In this paper, SVM is utilized in the 60-degree system. In multilevel SVM strategy in 60-degree system, at first,  $\alpha - \beta$  components of voltage are calculated [30,31]:

$$V_{\alpha}^* = V^* \cos(\theta) - \frac{V^* \sin(\theta)}{\sqrt{3}},$$

$$V_{\beta}^* = V^* \cos\left(\frac{\pi}{3} - \theta\right) - \frac{V^* \sin(\frac{\pi}{3} - \theta)}{\sqrt{3}}.$$

(1)

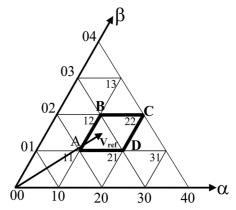

Afterwards, the foursquare, which the voltage vector is placed in (as shown in Figure 1), will be determined

**Figure 1.** Space vectors in the non-orthogonal 60-degree coordinate system.

| Phase voltage | Effect on            | FC of phase 'a' | Output voltage of phase | (S1,S1',S2,S2',S3,S3',<br>S4,S4',S5,S6,S7,S8)     |  |  |

|---------------|----------------------|-----------------|-------------------------|---------------------------------------------------|--|--|

| level         | $\overline{i_a > 0}$ | $i_a < 0$       | 'a' relative to "NP"    |                                                   |  |  |

| $V_0$         | 0                    | 0               | $-V_{dc}/2$             | (0,0,1,1,0,0,1,1,0,1,0,1)                         |  |  |

| $V_1$         | _                    | +               | $-V_{dc}/4$             | (0,0,1,1,0,0,1,1,0,1,1,0)                         |  |  |

| $V_2$         | +                    | _               | $-V_{dc}/4$             | $(0,\!0,\!1,\!1,\!0,\!0,\!1,\!1,\!1,\!0,\!0,\!1)$ |  |  |

| $V_3$         | 0                    | 0               | 0                       | (0,0,1,1,0,0,1,1,1,0,1,0)                         |  |  |

| $V_4$         | 0                    | 0               | 0                       | (1,1,0,0,1,1,0,0,0,1,0,1)                         |  |  |

| $V_5$         | _                    | +               | $V_{dc}/4$              | (1,1,0,0,1,1,0,0,0,1,1,0)                         |  |  |

| $V_6$         | +                    | _               | $V_{dc}/4$              | $(1,\!1,\!0,\!0,\!1,\!1,\!0,\!0,\!1,\!0,\!0,\!1)$ |  |  |

| $V_7$         | 0                    | 0               | $V_{dc}/2$              | (1,1,0,0,1,1,0,0,1,0,1,0)                         |  |  |

**Table 1.** Switching states of phase 'a' of 5-level ANPC.

using normalized values of  $V_{\alpha}$  and  $V_{\beta}$ :

$$A: (V_{A\alpha}, V_{A\beta}) = (V_{A\alpha} = \operatorname{int}(V_{\alpha}^*), V_{A\beta} = \operatorname{int}(V_{\beta}^*)),$$

$$B: (V_{B\alpha}, V_{B\beta}) = (V_{A\alpha}, V_{A\beta} + 1),$$

$$C: (V_{C\alpha}, V_{C\beta}) = (V_{A\alpha} + 1, V_{A\beta} + 1),$$

$$D: (V_{D\alpha}, V_{D\beta}) = (V_{A\alpha} + 1, V_{A\beta}). \tag{2}$$

After determining the vertices of the foursquare, the triangle of the voltage can be determined using amplitude of reference voltage vector and comparing it with the value of voltage vertices of foursquare (ABD or BCD) [30,31].

Switching times are calculated by utilizing  $T_s$ , the value of voltage vertices of the triangle and the amplitude of reference voltage. Typically, for BCD triangle, the system of equations contains three equations and three unknown switching times  $(T_B, T_C \text{ and } T_D)$ .

$$\begin{cases} V_{B\alpha}.T_B + V_{D\alpha}.T_D + V_{C\alpha}.T_C = V_{\alpha}^*.T_s \\ V_{B\beta}.T_B + V_{D\beta}.T_D + V_{C\beta}.T_C = V_{\beta}^*.T_s \\ T_B + T_D + T_C = T_s. \end{cases}$$

(3)

In each switching time period, according to the values of  $V_{\alpha}$  and  $V_{\beta}$ , final voltage vector (and status of the switches) will be determined via a pre-defined look-up table.

#### 3. Flying capacitors voltage balancing

In order to balance the voltages of flying capacitors, redundant voltage vectors related to ANPC should be investigated. According to the voltage vectors of ANPC, vectors of  $-V_{dc}/2$ , 0 and  $+V_{dc}/2$  have no effect on voltage of flying capacitors. Therefore, in intervals that these voltage vectors are implemented, flying capacitors voltages are kept constant.

Therefore, only redundant voltage vectors in the voltage levels of  $V_{dc}/4$  or  $-V_{dc}/4$  can be utilized in

order to stabilize flying capacitors voltages in  $V_{dc}/4$ . In intervals that voltage vectors of Vdc/4 or  $-V_{dc}/4$  are implemented, each flying capacitor voltage is compared with reference voltage of  $V_{dc}/4$ ; also phase current direction is determined. Therefore, according to flying capacitor voltage of each phase and the direction of each phase current, proper voltage vector can be selected using Table 1. For example, both of  $V_5$  and  $V_6$  produce voltage level of  $V_{dc}/4$  at the output; which for the positive current of the corresponding phase,  $V_5$  causes a decrease in the FC voltage and  $V_6$  causes an increase in the FC voltage. At the moment of implementing the voltage vector, according to the value of FC voltage, if it is needed to increase FC voltage,  $V_6$  is used and otherwise  $V_5$  is used.

#### 4. Neutral point voltage balancing

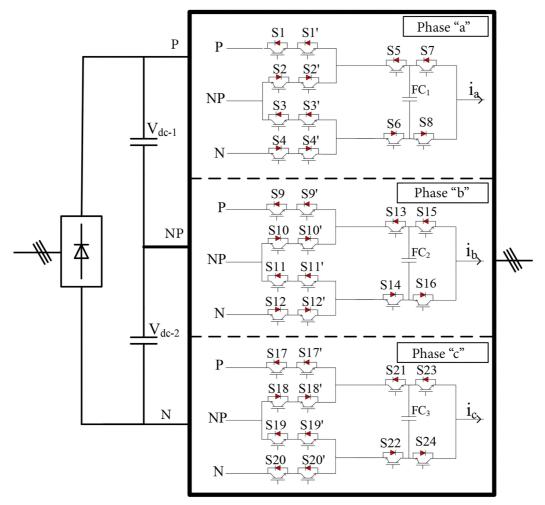

In order to balance the neutral point voltage, a lookup table based method is proposed for ANPC. The topology of the ANPC is shown in Figure 2. Redundant vectors are chosen in such a way to equate the upper half of dc-link voltage with lower half of dc-link voltage. This method will be added to the final section of SVM. In the final section of SVM, voltage vector will be selected from look-up table. According to the direction of each output phase current, selected voltage vector can lead to increment, decrement or noeffect on neutral point voltage. It should be noted that the lower half of dc-link voltage  $(V_{dc-2})$  will be compared with half of total dc-link voltage  $(V_{dc}/2)$  $(V_{dc}=V_{dc-1}+V_{dc-2})$ ; therefore if the lower half of dclink voltage  $(V_{dc-2})$  is lower than half of total dc-link voltage  $(V_{dc}/2)$  (in this condition, the upper half of dclink voltage  $(V_{dc-1})$  is more than half of total dc-link voltage), then the lower half of dc-link voltage  $(V_{dc-2})$ should be increased and lower half of dc-link voltage  $(V_{dc-2})$  should be decreased, and vice versa. In every iteration of SVM calculation, before utilizing look-up table, the proper look-up table (in order to balance the dc-link voltage) should be selected according to the

Figure 2. Five-level active NPC topology.

direction and absolute value of output phase currents and also increment or decrement of each half of dc-link voltage. The proper voltage vector will be obtained from this look-up table.

In the dc-link voltage balancing method, neutral point voltage can be assumed relative to both of positive rail  $(V_{dc-1})$  or negative rail  $(V_{dc-2})$ . In the following, in proposed method, NP voltage is assumed as  $V_{dc-2}$ .

In this method, in each data sampling, the value of three phase currents, and dc voltages are measured. According to the direction and absolute value of three phase currents in each sample, the operating point would be located in one of the following zones:

- 1.  $(i_{\alpha} > 0 \text{ and } |i_a| > |i_b| \text{ and } |i_a| > |i_c|)$

- 2.  $(i_{\alpha} < 0 \text{ and } |i_a| > |i_b| \text{ and } |i_a| > |i_c|)$

- 3.  $(i_b > 0 \text{ and } |i_b| > |i_c| \text{ and } |i_b| > |i_a|)$

- 4.  $(i_b < 0 \text{ and } |i_b| > |i_c| \text{ and } |i_b| > |i_a|)$

5.

$$(i_c > 0 \text{ and } |i_c| > |i_a| \text{ and } |i_c| > |i_b|)$$

6.

$$(i_c < 0 \text{ and } |i_c| > |i_a| \text{ and } |i_c| > |i_b|)$$

. (4)

Therefore, in each zone, two look-up tables should be determined; first for increment of neutral point voltage and second for decrement of neutral point voltage. According to identical look-up tables, there are six individual look-up tables for balancing the NP voltage. After determining the zone, in each sample, the proper look-up table should be selected according to the determined zone and also the need for increment or decrement of neutral point. The proper voltage vector will be obtained from this look-up table. Look-up tables are determined based on the following rules:

- 1. In zone 1:  $(|i_a| = |i_b + i_c| \text{ and } i_a > 0, i_b < 0, i_c < 0)$ , effect of selected phase 'a' voltage vector (in increasing or decreasing neutral point voltage) is more than two other phases ('b' or 'c'). This clause can be extended to zones 3 and 5;

- 2. In zone 2:  $(i_a| = |i_b + i_c| \text{ and } i_a < 0, i_b > 0, i_c > 0)$ , direction of phase currents is opposite in

comparison with zone 1. Therefore, look-up table which increases neutral point voltage in zone 2 is the same as look-up table which decreases neutral point voltage in zone 1. This clause can be extended to zones 4 and 6 (accordingly, there are 6 look-up tables in total);

- 3. Implementing voltage vectors of  $-V_{dc}/2$  or  $+V_{dc}/2$  in each phase has no effect on neutral point voltage.;

- 4. Implementing voltage vectors of -V<sub>dc</sub>/4 or +V<sub>dc</sub>/4 in each phase leads to different results depending on selected redundant voltage vector and direction of phase current. Implementing the first redundant voltage vector results in no-effect on neutral point voltage. Implementing second redundant voltage vector may result in increment or decrement of neutral point voltage depending on direction of phase current. If instantaneous value of phase current is negative, then neutral point voltage increases and vice versa;

- 5. Implementing voltage vectors of V<sub>3</sub> or V<sub>4</sub> in each phase leads to two different results depending on direction of phase current. If instantaneous value of phase current is negative, then neutral point voltage increases and vice versa. It should be noted that both of redundant voltage vectors have same effect on neutral point voltage.

For example, vector 032 ('0' for phase 'a', '3' for phase 'b' and 2 for phase 'c') in zone 1 is investigated to determine its effect on NP voltage. It should be noted that a number between 0 to 4 will be assigned to each phase; '0' means  $-V_dc^2$ , '1' means  $-V_{dc}/4$ , ... and '4' means  $+V_{dc}/2$ . In this zone, despite being  $i_a > 0$ , implementing  $-V_{dc}/2$  (or vector  $V_0$ ) in phase 'a' leads to no effect on NP voltage from phase 'a'. On the other hand,  $i_b$  is negative  $(i_b < 0)$  in zone 1, then using first redundant of  $+V_{dc}/4$  ( $V_5$ ) results in no-effect on NP voltage. Also second redundant of  $+V_{dc}/4$  ( $V_6$ ) leads to increment of NP voltage due to negative value of  $i_b$ . According to negative value of  $i_c$ , implementing both redundancies of vector 2 ( $V_3$  or  $V_4$ ) results in increasing the NP voltage. Consequently, phase 'a' has no effect on NP voltage, phase 'b' has no effect on NP voltage or leads to increment of NP voltage depending on the implementing redundant vector, and finally phase 'c' leads to increment of NP voltage. Therefore, vector 032 in zone 1 results in increment of NP voltage in total. It should be noted that this vector (032) in zone 2 has an opposite effect on NP voltage in comparison with zone 1. Accordingly, vector 032 in zone 2 results in decrement of NP voltage.

Six look-up tables which are used to increase or decrease the NP voltage in different zones are illustrated in Tables 2–7. These look-up tables are obtained via mentioned rules (1 through 5).

**Table 2.** A look-up table for increasing NP voltage in Zone 1 and decreasing NP voltage in Zone 2.

| $\alpha \beta$ | -4  | -3  | - <b>2</b> | -1  | 0   | 1   | 2   | 3   | 4   |

|----------------|-----|-----|------------|-----|-----|-----|-----|-----|-----|

| -4             |     |     |            |     | 044 | 043 | 042 | 041 | 040 |

| -3             |     |     |            | 034 | 033 | 032 | 031 | 030 | 140 |

| -2             |     |     | 024        | 023 | 022 | 021 | 020 | 130 | 240 |

| -1             |     | 014 | 013        | 012 | 011 | 010 | 120 | 341 | 340 |

| 0              | 004 | 003 | 002        | 001 | 000 | 443 | 442 | 441 | 440 |

| 1              | 104 | 103 | 102        | 434 | 433 | 432 | 431 | 430 |     |

| 2              | 204 | 314 | 424        | 423 | 422 | 421 | 420 |     |     |

| 3              | 304 | 414 | 413        | 412 | 411 | 410 |     |     |     |

| 4              | 404 | 403 | 402        | 401 | 400 |     |     |     |     |

**Table 3.** A look-up table for decreasing NP voltage in Zone 1 and increasing NP voltage in Zone 2.

| lphaeta | - <b>4</b> | -3  | - <b>2</b> | -1  | 0   | 1   | 2   | 3   | 4   |

|---------|------------|-----|------------|-----|-----|-----|-----|-----|-----|

| -4      |            |     |            |     | 044 | 043 | 042 | 041 | 040 |

| -3      |            |     |            | 034 | 144 | 143 | 142 | 141 | 140 |

| -2      |            |     | 024        | 134 | 244 | 243 | 242 | 241 | 240 |

| -1      |            | 014 | 124        | 234 | 233 | 232 | 231 | 230 | 340 |

| 0       | 004        | 114 | 224        | 223 | 222 | 221 | 220 | 330 | 440 |

| 1       | 104        | 214 | 213        | 212 | 211 | 210 | 320 | 430 |     |

| 2       | 204        | 203 | 202        | 201 | 200 | 310 | 420 |     |     |

| 3       | 304        | 303 | 302        | 301 | 300 | 410 |     |     |     |

| 4       | 404        | 403 | 402        | 401 | 400 |     |     |     |     |

**Table 4.** A look-up table for increasing NP voltage in Zone 3 and decreasing NP voltage in Zone 4.

| lphaeta | -4  | -3  | - <b>2</b> | -1  | 0   | 1   | 2   | 3   | 4   |

|---------|-----|-----|------------|-----|-----|-----|-----|-----|-----|

| -4      |     |     |            |     | 044 | 043 | 042 | 041 | 040 |

| -3      |     |     |            | 034 | 144 | 143 | 142 | 141 | 140 |

| -2      |     |     | 024        | 134 | 244 | 243 | 242 | 241 | 240 |

| -1      |     | 014 | 013        | 234 | 344 | 343 | 342 | 341 | 340 |

| 0       | 004 | 003 | 002        | 001 | 000 | 443 | 442 | 441 | 440 |

| 1       | 104 | 103 | 102        | 101 | 100 | 210 | 431 | 430 |     |

| 2       | 204 | 203 | 202        | 201 | 200 | 310 | 420 |     |     |

| 3       | 304 | 303 | 302        | 301 | 300 | 410 |     |     |     |

| 4       | 404 | 403 | 402        | 401 | 400 |     |     |     |     |

**Table 5.** A look-up table for decreasing NP voltage in Zone 3 and increasing NP voltage in Zone 4.

| $\alpha\beta$ | -4  | -3  | -2  | -1  | 0   | 1   | 2   | 3   | 4   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| -4            |     |     |     |     | 044 | 043 | 042 | 041 | 040 |

| -3            |     |     |     | 034 | 033 | 032 | 031 | 030 | 140 |

| -2            |     |     | 024 | 023 | 022 | 021 | 020 | 130 | 240 |

| -1            |     | 014 | 124 | 123 | 122 | 121 | 120 | 230 | 340 |

| 0             | 004 | 114 | 224 | 223 | 222 | 221 | 220 | 330 | 440 |

| 1             | 104 | 214 | 324 | 323 | 322 | 321 | 320 | 430 |     |

| 2             | 204 | 314 | 424 | 423 | 422 | 421 | 420 |     |     |

| 3             | 304 | 414 | 413 | 412 | 411 | 410 |     |     |     |

| 4             | 404 | 403 | 402 | 401 | 400 |     |     |     |     |

| $\alpha \beta$ | - <b>4</b> | -3  | - <b>2</b> | -1  | 0   | 1   | 2   | 3   | 4   |

|----------------|------------|-----|------------|-----|-----|-----|-----|-----|-----|

| -4             |            |     |            |     | 044 | 043 | 042 | 041 | 040 |

| -3             |            |     |            | 034 | 144 | 143 | 031 | 030 | 140 |

| -2             |            |     | 024        | 023 | 244 | 243 | 020 | 130 | 240 |

| -1             |            | 014 | 124        | 234 | 344 | 010 | 120 | 230 | 340 |

| 0              | 004        | 114 | 224        | 223 | 222 | 221 | 220 | 330 | 440 |

| 1              | 104        | 214 | 324        | 434 | 100 | 210 | 320 | 430 |     |

| 2              | 204        | 314 | 424        | 423 | 200 | 310 | 420 |     |     |

| 3              | 304        | 414 | 413        | 301 | 300 | 410 |     |     |     |

| 4              | 404        | 403 | 402        | 401 | 400 |     |     |     |     |

Table 6. A look-up table for increasing NP voltage in Zone 5 and decreasing NP voltage in Zone 6.

Table 7. Look-up table for decreasing NP voltage in Zone 5 and increasing NP voltage in Zone 6.

| $\alpha \beta$ | -4  | -3  | - <b>2</b> | -1  | 0   | 1   | 2   | 3   | 4   |

|----------------|-----|-----|------------|-----|-----|-----|-----|-----|-----|

| -4             |     |     |            |     | 044 | 043 | 042 | 041 | 040 |

| -3             |     |     |            | 034 | 033 | 032 | 142 | 141 | 140 |

| -2             |     |     | 024        | 134 | 022 | 132 | 242 | 241 | 240 |

| -1             |     | 014 | 013        | 012 | 122 | 232 | 342 | 341 | 340 |

| 0              | 004 | 003 | 002        | 112 | 444 | 443 | 442 | 441 | 440 |

| 1              | 104 | 103 | 102        | 212 | 322 | 432 | 431 | 430 |     |

| 2              | 204 | 203 | 202        | 312 | 422 | 421 | 420 |     |     |

| 3              | 304 | 303 | 302        | 412 | 411 | 410 |     |     |     |

| 4              | 404 | 403 | 402        | 401 | 400 |     |     |     |     |

It should be noted that a vector and its redundant vectors produce the same output line voltage. Therefore, there is no difference between a vector and its redundant vectors from viewpoint of output line voltage. It should be noted that selection of proper look-up table for NP voltage balancing would be done at the start of every SVM cycle (sample time); therefore no change between look-up tables would be done inside the SVM cycle.

#### 5. Experimental results

#### 5.1. Experimental setup

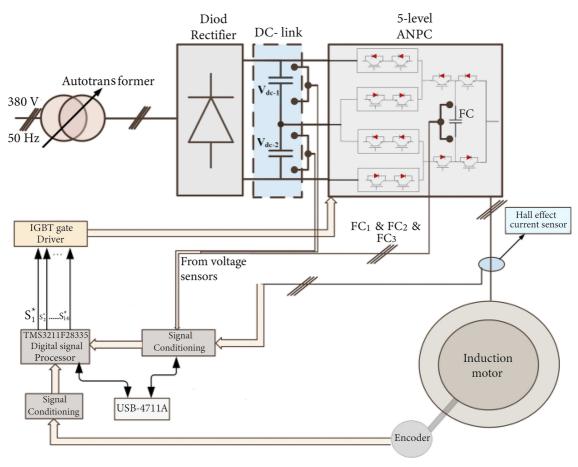

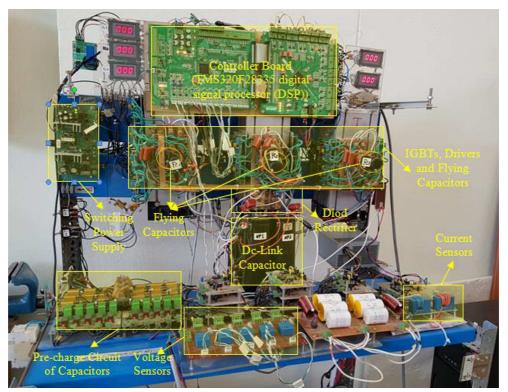

A laboratory setup is constructed in order to verify the applicability of the proposed method. The test setup configuration and experimental setup are illustrated in Figures 3 and 4. The experimental setup consists of controller board, IGBTs, IGBT drivers, flying capacitors, DC-link capacitors, Diod rectifier, voltage sensors, current sensors, switching power supply, and pre-charge circuit. The power circuit and the relation between different parts are shown in Figure 3. A float-point TMS320F28335 Digital Signal Processor (DSP) is used to implement the control algorithm. Also there are five

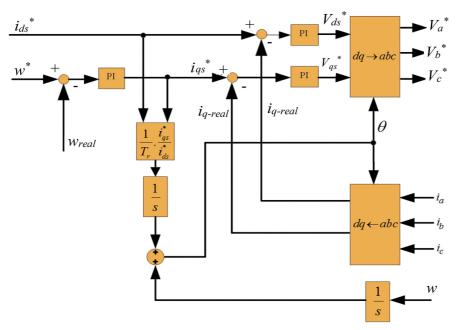

voltage sensors for three flying capacitors and two dclick capacitors. In addition, two current sensors are utilized for two of three phases. The switching power supply produces the ±15 V and 5 V for controller board. Results are sampled via an 'Advantech USB-4711A Data Acquisition' apparatus. In the experimental setup, the control method of induction motor is Rotor Field Oriented Control (RFOC). Block diagram of RFOC is shown in Figure 5. It should be noted that in ANPC converter, there are three independent switches in each phase. These switches include S1, S5 and S7 in phase 'a' (S9, S13 and S15 in phase 'b' and S17, S21 and S23 in phase 'c'). States of other switches can be determined via the states of these switches.

The sampling frequency of SVM is 1200 Hz. Induction motor parameters are shown in Table 8.

According to the procedure of voltage balancing (presented in Section 4), at first the operating zone should be determined; afterwards the proper look-up table according to operating zone should be selected. It should be noted that all of operations for dc-link voltage balancing includes basic logic operators such as 'and', 'or', 'not', etc.

Experimental tests are performed in two condi-

Figure 3. Test setup configuration.

Figure 4. Experimental setup.

| Table 8. Motor para  | meters. |

|----------------------|---------|

| $R_s (\Omega)$       | 3.0     |

| $R_r (\Omega)$       | 2.66    |

| $L_m$ (H)            | 0.179   |

| $L_{ls}$ (H)         | 0.0148  |

| $L_{lr}$ (H)         | 0.0148  |

| Number of pole pairs | 2       |

tions; "with NP voltage balancer" and "without NP voltage balancer" in high and low modulation indexes (high and low speed references).

Rated speed (rpm)

Rated power (kW)

1420

3

### 5.2. Case study 1: High modulation index

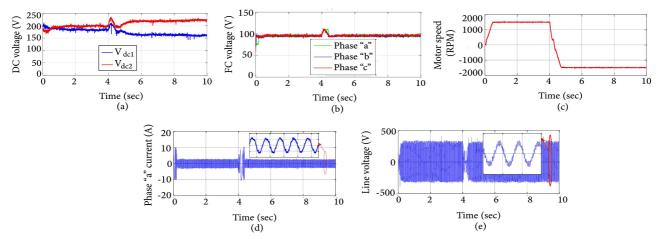

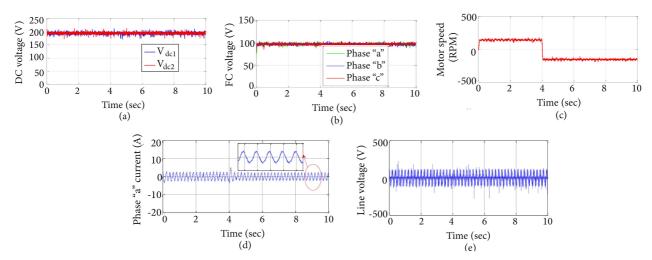

In this case, as shown in Figure 3, output dc voltage of the diod-rectifier is applied to the both ends of the full dc-link. In the first two tests (high modulation index), in both conditions of with or without NP balancer, the motor accelerates from standstill to 1500 rpm in a ramp wise manner; afterwards a speed command of -1500 rpm is applied to the motor at t=4 sec in a ramp wise manner (Figures 6 and 7). In results of Figures 6 and 7, upper half and lower half of the full dc-link voltages ( $V_{dc-1}$  and  $V_{dc-2}$ ), flying capacitor voltages of each phase and the motor speed are shown. In the condition of "without NP-voltage balancer", flying capacitor voltages of each phase are balanced properly;

Figure 5. Block diagram of rotor field-oriented control.

**Figure 6.** Performance of ANPC in the condition of "without NP balancer" -motor speed accelerates from standstill to 1500 rpm then reference speed varies to -1500 rpm at t = 4 sec in a ramp wise manner (a) Upper half and lower half of the full dc-link voltage; (b) Flying capacitor voltages of three phases; (c) Motor speed; (d) Motor current; and (e) Line voltage.

Figure 7. Performance of ANPC in the condition of "with NP balancer" - motor speed accelerates from standstill to 1500 rpm then reference speed varies to -1500 rpm at t = 4 sec in a ramp wise manner (a) Upper half and lower half of the full dc-link voltage; (b) Flying capacitor voltages of three phases; (c) Motor speed; (d) Motor current; and (e) Line voltage.

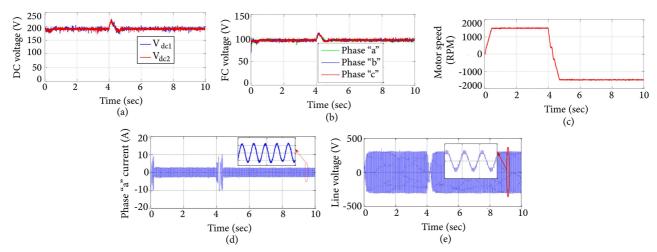

Figure 8. Performance of ANPC in the condition of "without NP balancer" in low modulation index- motor speed accelerates from standstill to 150 rpm then reference speed varies to -150 rpm at t = 4 sec in a ramp wise manner (a) Upper half and lower half of the full dc-link voltage; (b) Flying capacitor voltages of three phases; (c) Motor speed; (d) Motor current; (e) Line voltage.

but upper half and lower half of the full dc-link voltages  $(V_{dc-1} \text{ and } V_{dc-2})$  have significant difference.

In the condition of "with NP-voltage balancer", upper half and lower half of the full dc-link voltages and also flying capacitor voltages are balanced properly. Specifically, in the duration that motor speed decreases from 1500 rpm, full dc-link voltage increases due to regenerative mode of operation. In this duration, as shown in Figure 7, all of dc and FC voltages are also balanced properly according to the full dc-link voltage. In addition to proper performance, results show that the proposed method has proper dynamic response.

# 5.3. Case study 2: Low modulation index

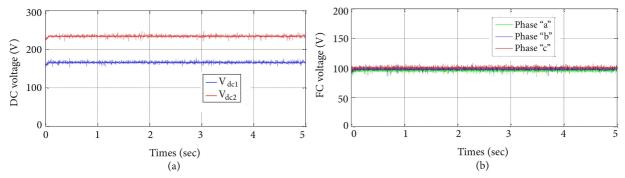

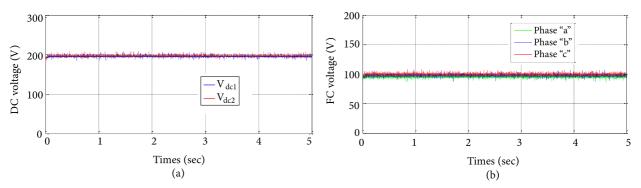

For the tests of low modulation index, the motor

accelerates from standstill to 150 rpm in a ramp wise manner; afterwards a speed command of -150 rpm is applied to the motor at t=4 sec in a ramp wise manner. Same as case study 1, in both conditions of with or without NP-voltage balancer, flying capacitors of three phases are balanced as shown in Figure 8(b) and Figure 9(b). As illustrated in Figure 8(a), in the condition of "without NP-voltage balancer", there is a significant difference between upper half and lower half of the dc-link voltages. But in the condition of "with NP-voltage balancer", the both half of dc-link voltages are balanced (Figure 9(a)).

It should be noted that tracking speed of capacitor voltage depends on switching frequency, capacitor value, instantaneous load current, and instantaneous output voltage vector.

Figure 9. Performance of ANPC in the condition of "with NP balancer" in low modulation index - motor speed accelerates from standstill to 150 rpm then reference speed varies to -150 rpm at t=4 sec in a ramp wise manner (a) Upper half and lower half of the full dc-link voltage; (b) Flying capacitor voltages of three phases; (c) Motor speed; (d) Motor current; (e) Line voltage.

Figure 10. Performance of ANPC in the condition of "without dc-link voltage balancer" under unbalanced loading - line voltage=110 V - fundamental frequency=25 Hz (a) Upper half and lower half of the full dc-link voltage and (b) Flying capacitor voltages of three phases.

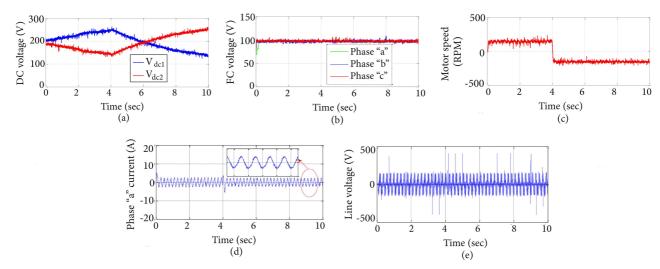

## 5.4. Case study 3: Under unbalanced load

In the proposed method, the process of neutral point voltage balancing depends on the instantaneous value and the direction of three phase currents which are measured in each sample. As the operating zone is determined via the instantaneous value of three phase currents, therefore the load imbalance does not disrupt the performance of the method.

Also, in order to evaluate the performance of proposed method under unbalanced load, three resistors of 30  $\Omega$ , 60  $\Omega$  and 90  $\Omega$  are utilized as three phase unbalanced load. In this test, output line voltage is 110 V and 25 Hz. As shown in the results of Figures 10 and 11, the flying capacitors are balanced in both conditions of with/without NP-voltage balancer. But there is a significant voltage imbalance between upper half and lower half of the dc-link voltage (Figure 10(a)) in the condition of "without NP-voltage balancer". As

shown in Figure 11(a), dc-link voltage is balanced by the proposed method of dc-link voltage balancer.

#### 6. Conclusion

In this paper, a look-up table-based and simplified method with proper implementation capability is proposed for controlling the Neutral-Point (NP) voltage in space vector modulation. In the proposed method, six different look-up tables are determined; these tables are selected in different operating conditions according to the direction of phase currents and comparison of  $V_{dc-1}$  and  $V_{dc-2}$ . Main advantage of the proposed method is its simplicity in implementation and low computing requirements; because just a few comparative operators are needed to determine the operating zone and requirement for increasing or decreasing the NP voltage.

Experimental results show that this method has proper performance and good dynamic response for

Figure 11. Performance of ANPC in the condition of "with dc-link voltage balancer" under unbalanced loading-line voltage=110 V - fundamental frequency=25 Hz (a) Upper half and lower half of the full dc-link voltage (b) Flying capacitor voltages of three phases.

balancing the NP voltage in low and high modulation indexes. Also other advantages of proposed method are less computational complexity and simplification of implementation.

## 7. Acknowledgment

The authors would like to thank Dr. Mustafa Mohamadian, Dr. Mohammad Arasteh, and Mr. Ali Keshavarzian for their comments and their assistance in experimental tests.

#### References

- Dekka, A., Wu, B., Yaramasu, V., et al. "Integrated model predictive control with reduced switching frequency for modular multilevel converters", *IET Elec*tric Power Applications, 11(5), pp. 857-863 (2017). DOI: 10.1049/iet-epa.2016.0454

- Kouro, S., Malinowski, M., Gopakumar, K., et al. "Recent advances and industrial applications of multilevel converters", *IEEE Transactions on Indus*trial Electronics, 57(8), pp. 2553-2580 (2010). DOI: 10.1109/TIE.2010.2049719

- Mukundan, N.M.C., Pychadathil, J., Subramaniam, U., et al. "Trinary hybrid cascaded H-bridge multilevel inverter-based grid-connected solar power transfer system supporting critical load", *IEEE Sys*tems Journal, 15(3), pp. 4116-4125 (2021). DOI: 10.1109/JSYST.2020.3025001

- Sánchez, J.A.P., Campos-Delgado, D.U., Espinoza-Trejo, D.R., et al. "Fault diagnosis in grid-connected PV NPC inverters by a model-based and data processing combined approach", IET Power Electronics, 12(12), pp. 3254-3264 (2019). DOI: 10.1049/iet-pel.2018.5237

- Soltani, M., Pairo, H., and Shoulaie, A. "Modelling approach for multi-carrier-based pulse-width modulation techniques utilised in asymmetrical cascaded H-bridge inverters", *IET Power Electronics*, 12(14), pp. 3822-3832 (2019). DOI: 10.1049/iet-pel.2019.0086

- 6. Rostami, H., Azizian, M.R., Davari, S.A., et al. "Single-phase three-level neutral-point-clamped inverter based on modified Z-source network with reduced voltage stress on capacitors", IEEE Journal of Emerging and Selected Topics in Power Electronics, 9(1), pp. 980-993 (2021). DOI: 10.1109/JESTPE.2020.2966286

- 7. Choudhury, A. and Pillay, P. "Space vector based capacitor voltage balancing for a three-level NPC traction inverter drive", *IEEE Journal of Emerging and Selected Topics in Power Electronics*, **8**(2), pp. 1276-1286 (2020). DOI: 10.1109/JESTPE.2019.2953183

- 8. Mukherjee, S., Giri, S., and Banerjee, S. "A flexible discontinuous modulation scheme with hybrid capacitor voltage balancing strategy for three-level NPC traction inverter", *IEEE Transactions on Industrial Electronics*, **66**(5), pp. 3333-3343 (2018). DOI: 10.1109/TIE.2018.2851967

- Yuan, Q., Li, A., Qian, J., et al. "DC-link capacitor voltage control for the NPC three-level inverter with a newly MPC-based virtual vector modulation", *IET Power Electronics*, 13(5), pp. 1093-1102 (2020). DOI: 10.1049/iet-pel.2019.0891.

- Zhong, L. and Hu, S. "A hybrid discontinuous PWM algorithm of balancing neutral point voltage for 3L-NPC inverter", *International Journal of Circuit Theory and Applications*, 49(12), pp. 1-22 (2021). DOI: 10.1002/cta.3079

- Farivar, G., Ghias, A.M.Y.M., Hredzak, B., et al. "Capacitor voltages measurement and balancing in flying capacitor multilevel converters utilizing a single voltage sensor", *IEEE Transactions on Power Electronics*, 32(10), pp. 8115-8123 (2017). DOI: 10.1109/TPEL.2016.2633278

- Stillwell, A., Candan, E., and Pilawa-Podgurski, R.C.N. "Active voltage balancing in flying capacitor multi-level converters with valley current detection and constant effective duty cycle control", *IEEE Transac*tions on Power Electronics, 34(11), pp. 11429-11441 (2019). DOI: 10.1109/TPEL.2019.2899899

- 13. Dekka, A., Wu, B., Fuentes, R.L., et al. "Voltage-balancing approach with improved harmonic performance for modular multilevel converters", *IEEE*

- Transactions on Power Electronics, **32**(8), pp. 5878-5884 (2017). DOI: 10.1109/TPEL.2017.2661245.

- 14. Ronanki, D. and Williamson, S.S. "New modulation scheme and voltage balancing control of modular multilevel converters for modern electric ships", *IET Power Electronics*, **12**(13), pp. 3403-3410 (2019). DOI: 10.1049/iet-pel.2018.6362.

- Dekka, A., Wu, B., Zargari, N.R., et al. "A space-vector PWM-based voltage-balancing approach with reduced current sensors for modular multilevel converter", *IEEE Transactions on Industrial Electronics*, 63(5), pp. 2734-2745 (2016). DOI: 10.1109/TIE.2016.2514346

- Bruckner, T., Bernet, S., and Guldner, H. "The active NPC converter and its loss-balancing control", IEEE Transactions on Industrial Electronics, 52(3), pp. 855-868 (2005). DOI: 10.1109/TIE.2005.847586.

- 17. Gurpinar, E., Yang, Y., Iannuzzo, F., et al. "Reliability-driven assessment of GaN HEMTs and Si IGBTs in 3L-ANPC PV inverters", *IEEE Journal of Emerging and Selected Topics in Power Electronics*, 4(3), pp. 956-969, (2016). DOI: 10.1109/JESTPE.2016.2566259.

- 18. Sheng, W. and Ge, Q. "A novel seven-level ANPC converter topology and its commutating strategies", *IEEE Transactions on Power Electronics*, **33**(9), pp. 7496-7509 (2018). DOI: 10.1109/TPEL.2017.2772885.

- Li, Y., Li, Y.W., Tian, H., et al. "A modular design approach to provide exhaustive carrier-based PWM patterns for multilevel ANPC converters", *IEEE Transactions on Industry Applications*, 55(5), pp. 5032-5044 (2019). DOI: 10.1109/TIA.2019.2928240.

- Wang, K., Zheng, Z., Xu, L., et al. "An optimized carrier-based PWM method and voltage balancing control for Five-Level ANPC converters", *IEEE Transactions on Industrial Electronics*, 67(11), pp. 9120-9132 (2020). DOI: 10.1109/TIE.2019.2956370

- Liu, F., Xu, L., Wang, K., et al. "CMV reduction for five-level ANPC converter by PS-PWM strategy", The Journal of Engineering, 2018(13), pp. 425-431, (2018). DOI: 10.1049/joe.2018.0020

- 22. Le, Q.A. and Lee, D. "Elimination of common-mode voltages based on modified SVPWM in five-level ANPC inverters", *IEEE Transactions on Power Electronics*, **34**(1), pp. 173-183 (2019). DOI: 10.1109/TPEL.2018.2825230

- 23. Davis, T.T. and Dey, A. "A neutral point voltage balancing scheme with improved transient performance for 5-Level ANPC and TNPC inverters", *IEEE Transactions on Power Electronics*, **34**(12), pp. 12513-12523 (2019). DOI: 10.1109/TPEL.2019.2908844

- 24. Siwakoti, Y.P., Mahajan, A., Rogers, D.J., et al. "A novel seven-level active neutral-point-clamped converter with reduced active switching devices and DC-Link voltage", *IEEE Transactions on Power Electronics*, **34**(11), pp. 10492-10508 (2019). DOI: 10.1109/TPEL.2019.2897061

- Wang, K., Xu, L., Zheng, Z., et al. "Capacitor voltage balancing of a five-level ANPC converter using phase-shifted PWM", *IEEE Transactions on Power Electronics*, 30(3), pp. 1147-1156, (2015). DOI: 10.1109/TPEL.2014.2320985

- Barbosa, P., Steimer, P., Meysenc, L., et al. "Active neutral-point-clamped multilevel converters", 36th Power Electronics Specialists Conference, Recife, pp. 2296-2301 (2005). DOI: 10.1109/PESC.2005.1581952

- 27. Pulikanti, S.R. and Agelidis, V.G. "Control of neutral point and flying capacitor voltages in five-level SHE-PWM controlled ANPC converter", 2009 4th IEEE Conference on Industrial Electronics and Applications, Xi'an, pp. 172-177 (2009). DOI: 10.1109/ICIEA.2009.5138191

- 28. Tan, G., Deng, Q. and Liu, Z. "An optimized SVPWM strategy for five-level active NPC (5L-ANPC) converter", *IEEE Transactions on Power Electronics*, 29(1), pp. 386-395 (2014). DOI: 10.1109/TPEL.2013.2248172

- Leon, J.I., Franquelo, L.G., Kouro, S., et al. "Simple modulator with voltage balancing control for the hybrid five-level flying-capacitor based ANPC converter", International Symposium on Industrial Electronics, Gdansk, pp. 1887-1892 (2011). DOI: 10.1109/ISIE.2011.5984445

- Arasteh, M., Abrishamifar A., and Dolatabadi, J.

"Fast SVM for a five level flying capacitor drive

with overvoltage reduction", 4th Annual International Power Electronics, Drive Systems and Technologies Conference, Tehran, pp. 188-192 (2013). DOI:

10.1109/PEDSTC.2013.6506701

- 31. Yao, W., Hu, H., and Lu, Z. "Comparisons of space-vector modulation and carrier-based modulation of multilevel inverter", *IEEE Transactions on Power Electronics*, **23**(1), pp. 45-51 (2008). DOI: 10.1109/TPEL.2007.911865

## **Biographies**

Hamidreza Pairo received his BS, and PhD degrees in Electrical Engineering from Iran University of Science and Technology (IUST), Tehran, Iran, in 2008 and 2017, respectively. Between 2013 and 2017, he was employed at the Iranian Research Institute of Electrical Engineering, where he was working on the design and construction of medium voltage high power drives. He is presently working as an Assistant Professor with Niroo Research Institute. His current research interests include high power drives, multilevel converters, multiphase motor drives, power electronics

and electrical machines.

Mohammad Farzi received the BS degree in electronic engineering from IUST University, Tehran, Iran, in 1996, and the ME degree in EMBA from IUST University, Tehran, Iran, in 2006. Currently, he

is the director of the research group of industrial power supply systems in ACECR. His current research interest is mainly power electronic topics such as power electronic converters, speed control of electric motors, traction system in metro trains, high current rectifiers and grid connected inverters.